Author(s)

, , , Nick Keller, Subhadeep Kal, Cheryl Alix, Aelen Mosden, Alain C. Diebold

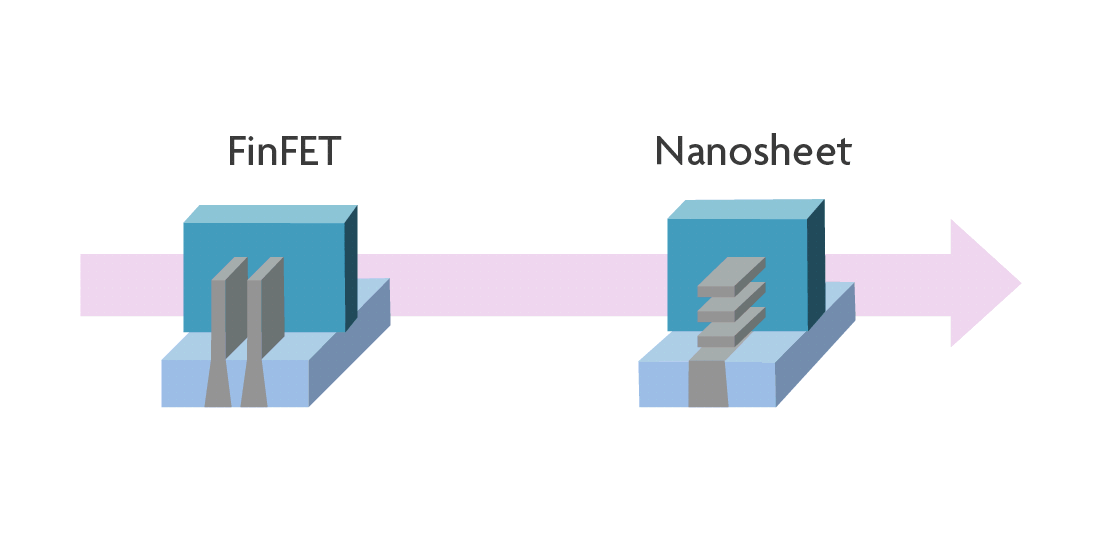

Nanosheet-based FET devices provide a non-planar device topology that advantageously enables improved control of short channel effects. A device including a stacked nanosheet field effect transistor (FET) may include a substrate, a first channel pattern on the substrate, a second channel pattern on the first channel pattern, a gate.

Abstract

The three-dimensional architectures for field effect transistors (FETs) with vertical stacking of Gate-all-Around Nanowires provide a pathway to increased device density and superior electrical performance. However, the transition from research into manufacturing will be successful only if their feature shape, critical dimensions, and associated electrical performance are repeatable across the integrated circuit, across the wafer, and among multiple wafers. Patterning process control for these structures will require significant advances in metrology. Two techniques that are potential candidates for this purpose are Mueller Matrix Spectroscopic Ellipsometry based Scatterometry (MMSE-scatterometry) and Critical Dimension Small Angle X-Ray Scattering (CDSAXS). In this work, we highlight the characterization of the Nanowire Test Structures fabricated from patterned Si/SixGe1-x/Si/SixGe1-x/Si/SixGe1-x/Si structures using CDSAXS. Preliminary experimental data shows sensitivity to the selective etching of subsurface SixGe1-x. CDSAXS diffraction data provides information in reciprocal space about line shape and periodicity as well as the amount of subsurface etching. Side lobes in the Intensity vs. Qz (structure height) data are observed around Qz positions of around 0.15 nm-1 and 0.5 nm-1 and are at the same positions in the measured, and the simulated data for different amounts of SixGe1-x etch in the Nanowire Test Structures. This demonstrates its ability for successful measurement of the critical dimensions and 3D profile of the Nanowire Test Structures, which can then be extended to monitor several key process steps for Nanowire/Nanosheet FET fabrication..jpg)

February 24-28, 2020

Nano Sheet

San Jose, CA

SPIE Advanced Lithography

Huiming Bu

Conferences

Nanosheet Finfet Fabrication Process

Finfet Transistors

Citation